## SONY

# CXD1179Q

### 8-bit 35MSPS Video A/D Converter with Clamp Function

#### Description

The CXD1179Q is an 8-bit CMOS A/D converter for video with synchronizing clamp function. The adoption of 2 step-parallel method achieves ultra-low power consumption and a maximum conversion speed of 35MSPS.

#### Features

- Resolution: 8-bit ± 1/2LSB (DL)

- Maximum sampling frequency: 35MSPS

- Low power consumption: 80 mW (at 35MSPS typ.) (reference current excluded)

- Synchronizing clamp function

- Clamp ON/OFF function

- Reference voltage self bias circuit

- Input CMOS compatible

- 3-state TTL compatible output

- Single 5V power supply

- Low input capacitance: 8 pF

- Reference impedance: 330  $\Omega$  (typ.)

#### Applications

Wide range of applications that require high-speed A/D conversion such as TV and VCR.

#### Structure

Silicon gate CMOS IC

#### Absolute Maximum Ratings (Ta=25 °C)

- Supply voltage VDD 7

- Reference voltage

- VRT, VRB VDD + 0.5 to Vss 0.5 V

V

- Input voltage VIN VDD + 0.5 to Vss 0.5 V (Analog)

- Input voltage VI VDD + 0.5 to Vss 0.5 V (Digital)

- Output voltage Vo VDD + 0.5 to Vss 0.5 V (Digital)

- Storage temperature

- Tstg –55 to +150 °C

#### **Recommended Operating Conditions**

- Supply voltage AVDD, AVss 4.75 to 5.25 V

- DVdd, DVss

- | DVss AVss | 0 to 100 mV

- Reference input voltage

- VRB 0 and above V

- VRT 2.7 and below V

- Analog input VIN 1.8 Vp-p above

- Clock pulse width

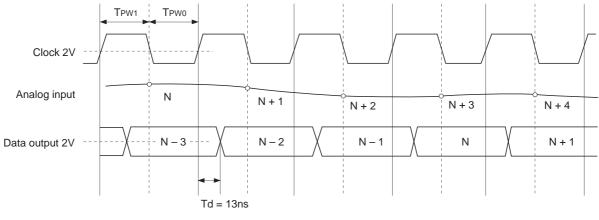

- Tpw1, Tpw0 13 ns (min) to 1.1 µs (max)

- Operating ambient temperature

- Topr -40 to +85 °C

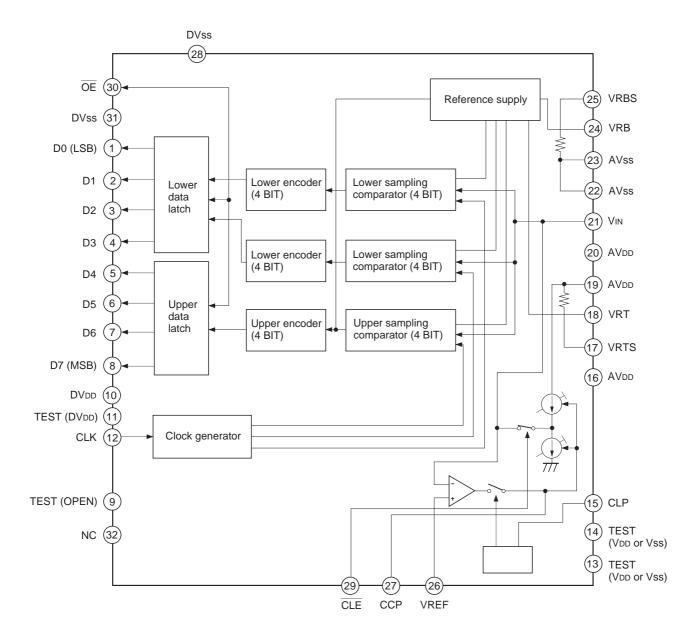

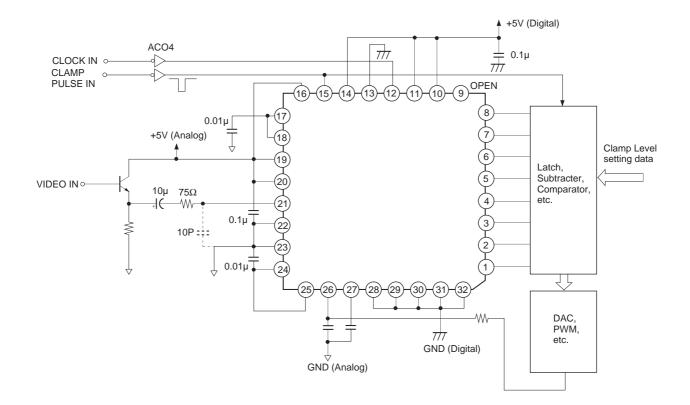

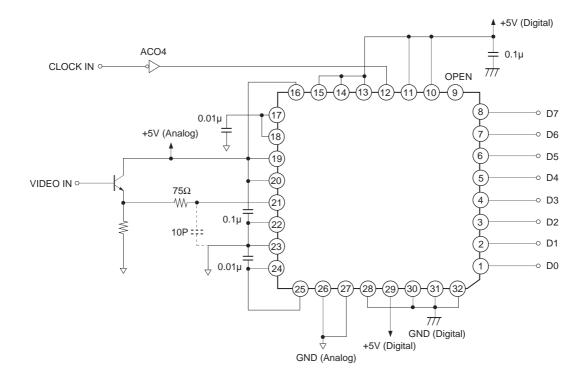

#### **Block Diagram**

#### **Pin Description**

| Pin No.    | Symbol   | Equivalent circuit                          | Description                                                             |

|------------|----------|---------------------------------------------|-------------------------------------------------------------------------|

| 1 to 8     | D0 to D7 |                                             | D0 (LSB) to D7 (MSB) output                                             |

| 9          | TEST     | 9                                           | Leave open during normal usage.                                         |

| 10         | DVdd     |                                             | Digital +5 V                                                            |

| 12         | CLK      | 12<br>DVDD<br>(12<br>DVss                   | Clock input                                                             |

| 11, 13, 14 | TEST     | DVDD<br>(1)<br>(13)<br>(14)<br>DVss<br>DVss | Fix Pin 11 to VDD, Pins 13 and 14 to<br>VDD or Vss during normal usage. |

—3—

| Pin No.    | Symbol | Equivalent circuit  | Description                                                                              |  |  |

|------------|--------|---------------------|------------------------------------------------------------------------------------------|--|--|

| 15         | CLP    | DVDD<br>15<br>DVSS  | Inputs clamp pulse to Pin 15 (CLP).<br>Clamps the signal voltage during Low<br>interval. |  |  |

| 16, 19, 20 | AVdd   |                     | Analog +5 V                                                                              |  |  |

| 17         | VRTS   | AVDD                | Generates about +2.6 V when shorted with VRT.                                            |  |  |

| 18         | VRT    |                     | Reference voltage (top)                                                                  |  |  |

| 24         | VRB    | (18) (24)<br>AVss   | Reference voltage (bottom)                                                               |  |  |

| 21         | Vin    | AVDD<br>(2)<br>AVSS | Analog input                                                                             |  |  |

| 22, 23     | AVss   |                     | Analog ground                                                                            |  |  |

| 25         | VRBS   | AVss<br>25          | Generates about +0.6 V when shorted with VRB.                                            |  |  |

—4—

| Pin No. | Symbol | Equivalent circuit                   | Description                                                                                                                                                                                                                                                                                                                                          |

|---------|--------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26      | VREF   | AVDD<br>26<br>W<br>AVss              | Clamp reference voltage input.<br>Clamps so that the reference voltage<br>and the input signal during clamp<br>interval are equal.                                                                                                                                                                                                                   |

| 27      | ССР    | AVDD<br>27<br>AVss                   | Integrates the clamp control voltage.<br>The relationship between the changes<br>in CCP voltage and in VIN voltage is<br>positive phase.                                                                                                                                                                                                             |

| 28, 31  | DVss   |                                      | Digital ground                                                                                                                                                                                                                                                                                                                                       |

| 29      | CLE    | DVDD<br>29<br>CLAMP<br>DVss<br>PULSE | The clamp function is enabled when<br>$\overline{\text{CLE}}$ = Low.<br>The clamp function is set to off and<br>the converter functions as a normal<br>$A/D$ converter when $\overline{\text{CLE}}$ = High.<br>The clamp pulse can be measured by<br>connecting $\overline{\text{CLE}}$ to $DV_{DD}$ through a<br>several hundred $\Omega$ resistor. |

| 30      | ŌĒ     | 30<br>DVDD<br>30<br>DVss             | Data is output when $\overline{OE}$ = Low.<br>Pins D0 to D7 are at high impedance<br>when $\overline{OE}$ = High.                                                                                                                                                                                                                                    |

| 32      | NC     |                                      | NC pin                                                                                                                                                                                                                                                                                                                                               |

—5—

#### **Digital Output**

The following table shows the relationship between analog input voltage and digital output code.

| Input signal<br>voltage | Step | Digital output code<br>MSB LSB |

|-------------------------|------|--------------------------------|

| Vrt                     | 0    | 1 1 1 1 1 1 1 1                |

| :                       | :    | :                              |

| :                       | 127  | 10000000                       |

| :                       | 128  | 0 1 1 1 1 1 1 1                |

| :                       | :    | :                              |

| Vrb                     | 255  | 00000000                       |

• : Analog signal sampling point

**Timing Chart II.**

#### **Electrical Characteristics**

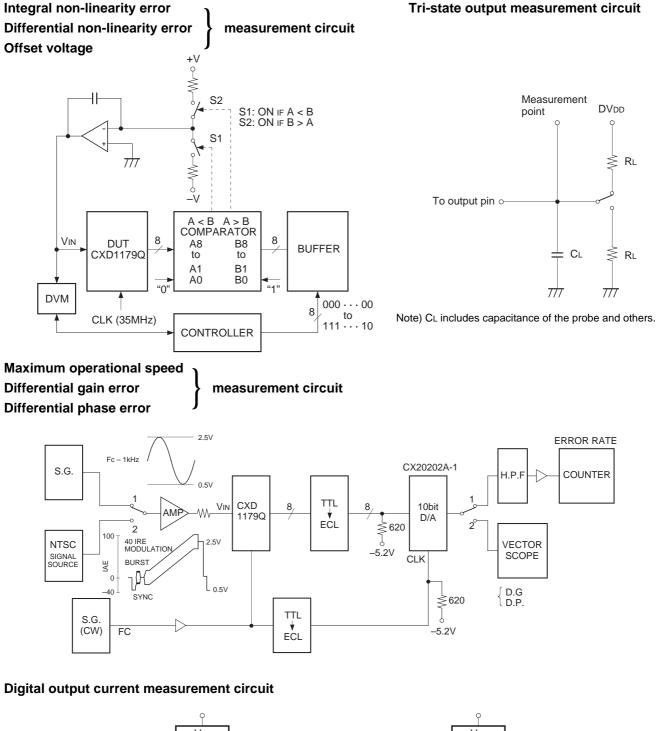

#### Analog characteristics

#### (Fc = 35MSPS, Vdd = 5 V, Vrb = 0.5 V, Vrt = 2.5 V, Ta = 25 °C)

| Item                               | Symbol      | Con                                                                                                        | ditions                     | Min. | Тур. | Max.         | Unit |

|------------------------------------|-------------|------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|--------------|------|

| Conversion speed                   | Fc          | $V_{DD} = 4.75 \text{ to } 5.25 \text{ V}$<br>Ta = -40 to +85 °C<br>VIN = 0.5 to 2.5 V<br>fIN = 1 kHz ramp |                             | 0.5  |      | 35           | MSPS |

| Analog input band width<br>(-1 dB) | BW          | Envelope                                                                                                   |                             |      | 25   |              | MHz  |

| Offeet veltere*1                   | Еот         | Potential differ                                                                                           | Potential difference to VRT |      | -40  | -20          | mV   |

| Offset voltage*1                   | Еов         | Potential difference to VRB                                                                                |                             | +55  | +75  | +95          |      |

| Integral non-linearity error       | EL          | End point                                                                                                  |                             |      | +0.5 | +1.3<br>-1.0 | LSB  |

| Differential non-linearity error   | ED          |                                                                                                            |                             |      | ±0.3 | ±0.5         |      |

| Differential gain error            | DG          | NTSC 40 IRE mod ramp                                                                                       |                             |      | 1    |              | %    |

| Differential phase error           | DP          | Fc = 14.3MSPS                                                                                              |                             |      | 0.5  |              | deg  |

| Aperture jitter                    | taj         |                                                                                                            |                             |      | 30   |              | ps   |

| Sampling delay                     | tsd         |                                                                                                            |                             |      | 2    |              | ns   |

| Oleman effect welter as *2         | <b>F</b> aa |                                                                                                            | Vref = 0.5 V                | -20  | 0    | +20          | - mV |

| Clamp offset voltage*2             | Eoc         |                                                                                                            | Vref = 2.5 V                | -30  | -10  | +10          |      |

| Clamp pulse delay                  | tcpd        |                                                                                                            |                             |      | 25   |              | ns   |

\*1 The offset voltage EOB is a potential difference between VRB and a point of position where the voltage drops equivalent to 1/2 LSB of the voltage when the output data changes from "00000000" to "00000001". EOT is a potential difference between VRT and a potential of point where the voltage rises equivalent to 1/2LSB of the voltage when the output data changes from "11111111" to "11111110".

\*2 Clamp offset voltage varies individually. When using with R, G, B 3 channels, color sliding may be generated.

#### **DC** characteristics

(Fc = 35MSPS, VDD = 5 V, VRB = 0.5 V, VRT = 2.5 V, Ta = 25 °C)

| Item                                 | Symbol      | Conditions                                 |                           | Min. | Тур. | Max. | Unit |

|--------------------------------------|-------------|--------------------------------------------|---------------------------|------|------|------|------|

| Supply current                       | IDD         | Fc = 35MSPS<br>NTSC ramp wave input        |                           |      | 16   | 22   | mA   |

| Reference pin current                | IREF        |                                            |                           | 4.5  | 6.1  | 8.7  | mA   |

| Analog input capacitance             | CIN         | VIN = 1.5 V ·                              | + 0.07 Vrms               |      | 8    |      | pF   |

| Reference resistance<br>(VRT to VRB) | Rref        |                                            |                           | 230  | 330  | 440  | Ω    |

| Colf biog I                          | VRB1        | Shorts VRB and VRBS<br>Shorts VRT and VRTS |                           | 0.52 | 0.56 | 0.60 | V    |

| Self-bias I                          | Vrt1 – Vrb1 |                                            |                           | 1.96 | 2.10 | 2.24 |      |

| Self-bias II                         | Vrt2        | VRB = AGND<br>Shorts VRT and VRTS          |                           | 2.13 | 2.33 | 2.53 | V    |

| Disital input valtage                | Viн         | VDD = 4.75 to 5.25 V<br>Ta = -40 to +85 °C |                           | 3.5  |      |      | v    |

| Digital input voltage                | VIL         |                                            |                           |      |      | 0.5  |      |

| Disital issue as a second            | Ін          |                                            | Vih = Vdd                 |      |      | 5    |      |

| Digital input current                | lı∟         | - VDD = max                                | VIL = 0 V                 |      |      | 5    | μA   |

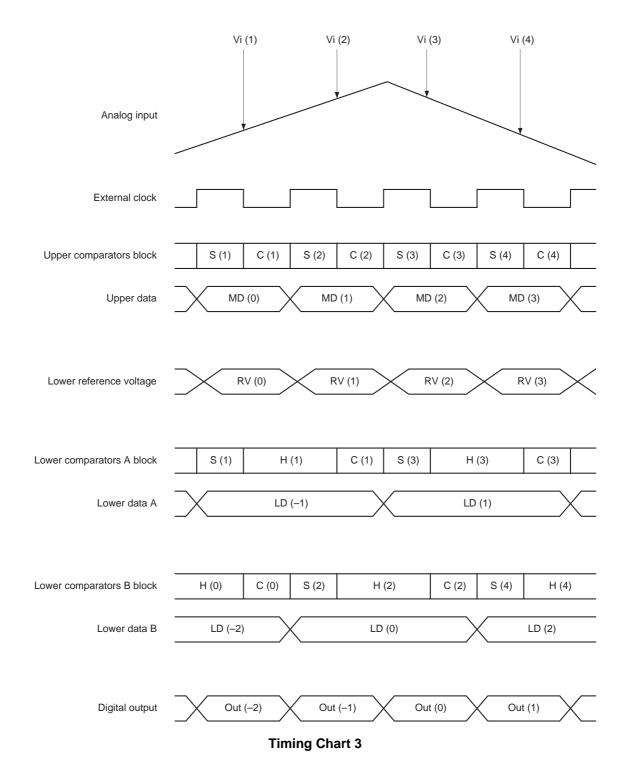

|                                      | Іон         | OE = Vss<br>Vdd = min                      | $V_{OH} = V_{DD} - 0.5 V$ | -1.1 | -2.5 |      |      |

|                                      | IOL         |                                            | Vol = 0.4 V               | 3.7  | 6.5  |      | mA   |

| Digital output current               | Іоzн        | $\overline{OE} = V_{DD}$ $V_{DD} = max$    | Voh = Vdd                 |      |      | 16   |      |

|                                      | Iozl        |                                            | Vol = 0 V                 |      |      | 16   | μA   |

#### Timing

(Fc = 35MSPS, Vdd = 5 V, Vrb = 0.5 V, Vrt = 2.5 V, Ta = 25 °C)

| Item                             | Symbol       | Conditions                                                                                                                                                                                                                                            | Min. | Тур. | Max. | Unit |

|----------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Output data delay                | Tol          | With TTL 1 gate and 10 pF load<br>$V_{DD} = 4.75$ to 5.25 V<br>Ta = -40 to +85 °C                                                                                                                                                                     | 7    | 13   | 18   | ns   |

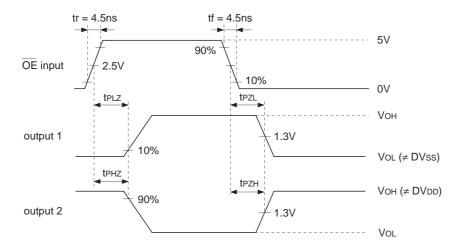

| Tri-state output<br>enable time  | tрzн<br>tpzL | $\begin{array}{l} {R_{\text{L}}=1\ \text{k}\Omega,\ \text{C}_{\text{L}}=15\ \text{pF}}\\ \hline {OE}=5\ \text{V}\to 0\ \text{V}\\ \text{V}_{\text{DD}}=4.75\ \text{to}\ 5.25\ \text{V}\\ \text{Ta}=-40\ \text{to}\ +85\ ^{\circ}\text{C} \end{array}$ | 5    | 8    | 14   | ns   |

| Tri-state output<br>disable time | tphz<br>tplz | $\begin{array}{l} R_L = 1 \ k\Omega, \ C_L = 15 \ pF\\ \hline OE = 0V \rightarrow 5 \ V\\ V_{DD} = 4.75 \ to \ 5.25 \ V\\ Ta = -40 \ to \ +85 \ ^\circC \end{array}$                                                                                  | 4    | 6.5  | 11   | ns   |

| Clamp pulse width*1              | tcpw         | Fc = 14MSPS, CIN = 10 $\mu$ F for NTSC wave                                                                                                                                                                                                           | 1.75 | 2.75 | 3.75 | μs   |

\*1 The clamp pulse width is for NTSC as an example. Adjust the rate to the clamp pulse cycle (1/15.75 kHz for NTSC) for other processing systems to equal the values for NTSC.

#### **Electrical Characteristics Measurement Circuit**

**Operation** (See Block Diagram and Timing Chart 3)

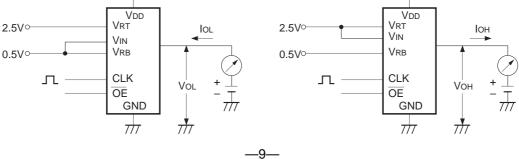

The CXD1179Q is a 2-step parallel system A/D converter featuring a 4-bit upper comparators group and 2 lower comparators groups of 4-bit each. The reference voltage that is equal to the voltage between VRT – VRB/16 is constantly applied to the upper 4-bit comparator block. Voltage that corresponded to the upper data is fed through the reference supply to the lower data. VRTS and VRBS pins serve for the self generation of VRT (Reference voltage top) and VRB (Reference voltage bottom).

- This IC uses an offset cancel type comparator and the comparator operates synchronously with an external clock. These modes are respectively indicated on the timing chart with S, H, C symbols. That is, the comparator performs input sampling (auto zero) mode, input hold mode and comparison mode using the external clock.

- 3. The operation of respective parts is as indicated in the chart. For instance input voltage Vi (1) is sampled with the falling edge of the first clock by means of the upper comparator block and the lower comparator A block.

The upper comparators block finalizes comparison data MD (1) with the rising edge of the first clock. Simultaneously the reference supply generates the lower reference voltage RV (1) that corresponded to the upper results. The lower comparator block finalizes comparison data LD (1) with the rising edge of the second clock. MD (1) and LD (1) are combined and output as Out (1) with the rising edge of the 3rd clock. Accordingly there is a 2.5 clock delay from the analog input sampling point to the digital data output.

#### **Operation Notes**

1. Power supply and ground

To reduce noise effects, separate the analog and digital systems close to the device. For both the digital and analog power supply pins, use a ceramic capacitor of about 0.1  $\mu$ F set as close as possible to the pin to bypass to the respective grounds.

2. Analog input

Compared with the flash type A/D converter, the input capacitance of the analog input is rather small. However it is necessary to conduct the drive with an amplifier featuring sufficient band and drive capability. When driving with an amplifier of low output impedance, parasite oscillation may occur. That may be prevented by inserting a resistance of about 100  $\Omega$  in series between the amplifier output and A/D input.

3. Clock input

The clock line wiring should be as short as possible also, to avoid any interference with other signals, separate it from other circuits.

4. Reference input

Voltage between VRT to VRB is compatible with the dynamic range of the analog input. Bypassing VRT and VRB pins to analog ground, by means of a capacitor about 0.1  $\mu$ F, the stable characteristics of the reference voltage are obtained. By shorting VRT and VRTS, VRB and VRBS, the self-bias function that generates VRT = about 2.6 V and VRB = about 0.6 V, is activated.

5. Timing

Analog input is sampled with the falling edge of CLK and output as digital data with a delay of 2.5 clocks and with the following rising edge. The delay from the clock rising edge to the data output is about 13ns.

6. OE pin

By connecting OE to DVss output mode is obtained. By connecting OE to DVpb high impedance is obtained.

#### **Application Circuit**

#### (1) When clamp is used (self bias used)

\* The clamp pulse is latched by the sampling clock of ADC, but that is not necessary for basic clamp operation. However, slight small beat may be generated as vertical sag according to the relationship between the sampling frequency and the clamp pulse frequency. At such time, the latch circuit is effective in this case.

#### (2) Digital clamp (self bias used)

#### (3) When clamp is not used (self bias used)

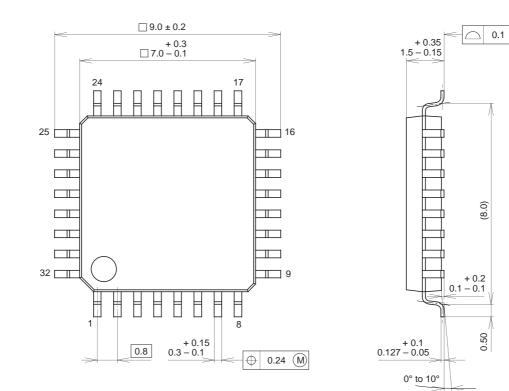

Package Outline Unit : mm

#### 32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP032-P-0707 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE MASS     | 0.2g           |

(8.0)

0.50